## MODELLIZZAZIONE CIRCUITALE DI VIAS SU CIRCUITI STAMPATI MULTISTRATO

Francesco de Paulis<sup>1</sup>, Jun Fan<sup>2</sup>, James Drewniak<sup>2</sup>, Antonio Orlandi<sup>1</sup>, Bruce Archambeault<sup>3</sup>, Xiaoxiong Gu<sup>4</sup>

<sup>1</sup>UAq EMC Laboratory, Dip. di Ingegneria Elettrica e dell'Informazione,

Università degli Studi dell'Aquila, Via Campo di Pile, 67100, L'Aquila (AQ)

<sup>2</sup>Missouri University of Science and Technology, Rolla, MO, USA

<sup>3</sup>IBM Systems and Technology Group RTP, NC, USA

<sup>4</sup>IBM T.J. Watson Research Center, NY, USA

I moderni sistemi digitali prevedono migliaia di interconnessioni per la trasmissione di dati su circuiti stampati multistrato (Printed Circuit Board - PCB). Ciò crea la necessità di utilizzare fori di vias (o più semplicemente vias) per permettere il passaggio dei segnali su layer diversi. Le vias possono creare problemi all'integrità del segnale trasmesso su di esse in quanto creano una discontinuità al percorso del segnale su microstrip/stripline.

L'analisi degli effetti del via può essere studiata tramite simulatori elettromagnetici 3D; tale scelta, però, richiede la creazione del modello e tempi di simulazione molto lunghi. La creazione di modelli circuitali equivalenti, che possano rappresentare in modo accurato il comportamento elettrico del via, è di primaria importanza per una simulazione più veloce e utile in fase di progettazione o di analisi.

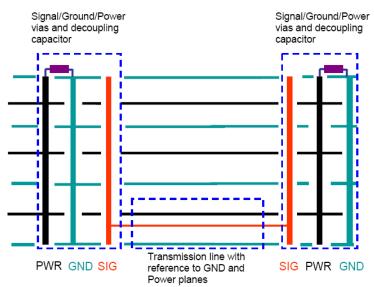

Il modello circuitale sviluppato consente di includere gli effetti della transizione del via, gli effetti dovuti alla propagazione del campo elettromagnetico all'interno delle cavità (generate da due piani continui adiacenti) attraversate dal via stesso, gli effetti delle transizioni da via a stripline. Di conseguenza il link di segnale che va da driver a receiver posizionati sui layer esterni può essere modellizzato completamente, come nell'esempio di Fig.1 (linea rossa). Il modello tiene conto anche di altri vias presenti nella PCB, sia relativi ad altri segnali, sia relativi a connessioni di power (PWR) o di ground (GND), linee di colore nero e azzurro in

Fig. 1. Sezione trasversale di una PCB multistrato con vias, stripline, condensatori di disaccoppiamento, cavità formate dai piani di PWR e GND.

Fig. 1, rispettivamente.

condensatori di disaccoppiamento (decoupling capacitors) vengono di solito posizionati sul PCB per ridurre la propagazione del rumore tra i piani di alimentazione; quindi fanno parte delle problematiche relative all'accoppiamento del rumore tra vias e cavità. Il modello circuitale del vias recentemente sviluppato permette di includere anche dei condensatori l'effetto disaccoppiamento (rettangoli viola in Fig. 1).

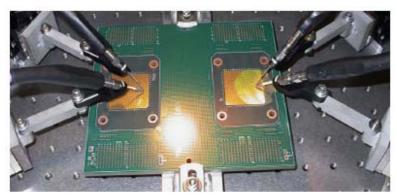

Il modello in esame è stato testato confrontando i risultati della simulazione circuitale (implementata in ambiente Matlab) con risultati sperimentali. Alcune board di test sono state realizzate ad hoc per la verifica dell'accuratezza del modello proposto, includendo sia vias di segnale, sia di PWR e GND. Una delle board di test è riportata in Fig. 2, in cui sono presenti due footprint per

Fig. 2. Link differenziali tra due footprint BGA

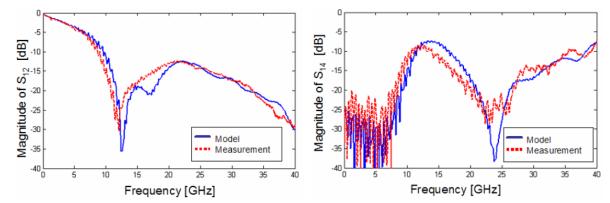

componenti BGA (ball grid array) e quindici coppie di stripline differenziali vanno da coppie di vias di un footprint, a coppie di vias sull'altro footprint. La stessa geometria è stata simulata dopo aver sviluppato il circuito equivalente basato sul metodo risultati proposto. confronti misure-simulazioni sono riportati in Fig. 3. Il modello equivalente

ottimo accordo con i dati misurati, dando quindi ampia affidabilità al metodo proposto.

Fig. 3.  $|S_{12}|$  and  $|S_{14}|$  of one of the stripline differential link. Model vs. measurement.

## Referenze

- [1] X. Gu, R. R. imolo-Donadio, Z. Yu, F. de Paulis, Y. H. Kwark, M. Cocchini, M. B. Ritter, B. Archambeault, A. Ruehli, J. Fan, C. Schuster, "Fast Physics-Based Via and Trace Models for Signal and Power Integrity Co-Analysis," *in Proc. IEC DesignCon 2010*, February 1-4, 2010, Santa Clara, USA.

- [2] R. Rimolo-Donadio, X. Gu, Y. H. Kwark, M. B. Ritter, B. Archambeault, F. De Paulis, et al., "Physics-based via and trace models for efficient link simulation on multilayer structures up to 40 GHz," *IEEE Transaction on Microwave Theory and Techniques*, vol. 57, no. 8, pp. 2072-2083, August 2009.

- [3] V. Ricchiuti, F. de Paulis, A. Orlandi, "An equivalent circuit model for the identification of the stub resonance due to differential vias on PCB," *in Proc. IEEE Workshop on Signal Propagation on Interconnects* 2009, SPI '09, May 12-15, 2009, Strasbourg France.

- [4] X. Gu, F. De Paulis, et al., "Fully analytical methodology for fast end-to-end link analysis on complex printed circuit boards including signal and power integrity effects"," *in Proc. IEC DesignCon 2009*, February 2-5, 2009, Santa Clara, USA.